PXA255 RISC based PC/104 Single Board Computer

**Technical Manual**

#### Definitions

Arcom is the trading name for Arcom Control Systems Inc and Arcom Control Systems Ltd.

#### Disclaimer

The information in this manual has been carefully checked and is believed to be accurate. Arcom assumes no responsibility for any infringements of patents or other rights of third parties, which may result from its use.

Arcom assumes no responsibility for any inaccuracies that may be contained in this document. Arcom makes no commitment to update or keep current the information contained in this manual.

Arcom reserves the right to make improvements to this document and/or product at any time and without notice.

#### Warranty

This product is supplied with a 3 year limited warranty. The product warranty covers failure of any Arcom manufactured product caused by manufacturing defects. The warranty on all third party manufactured products utilized by Arcom is limited to 1 year. Arcom will make all reasonable effort to repair the product or replace it with an identical variant. Arcom reserves the right to replace the returned product with an alternative variant or an equivalent fit, form and functional product. Delivery charges will apply to all returned products. Please check <u>www.arcom.com/support</u> for information about Product Return Forms.

#### Trademarks

ARM and StrongARM are registered trademarks of ARM Ltd.

Intel and XScale are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

Windows CE is a trademark of the Microsoft Corporation.

CompactFlash is the registered trademark of SanDisk Corp.

Linux is a registered trademark of Linus Torvalds.

RedBoot and Red Hat<sup>™</sup> is a registered trademark of Red Hat Inc.

VxWorks is a register trademark of Wind River.

Bluetooth is a registered trademark of Bluetooth SIG, Inc.

All other trademarks recognized.

#### **Revision History**

| Manual  | PCB         | Date                          | Comments                                                                                                                  |

|---------|-------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Issue A | V2 Issue 3  | 29 <sup>th</sup> June 2005    | First full release of Manual for VIPER Version 2.                                                                         |

| Issue B | V2 Issue 4A | 9 <sup>th</sup> August 2006   | Updated to include VIPER-Lite details, support for Intel P30<br>Flash, and for full RoHS-6 compliance.                    |

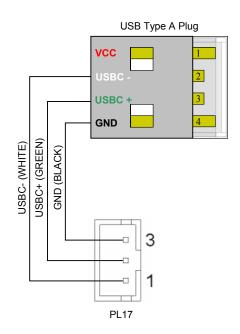

| Issue C | V2 Issue 4A | 25 <sup>th</sup> January 2007 | Updated to show USB cables with Type A Plugs used to connect to USB Host and Client connectors PL7 and PL17 respectively. |

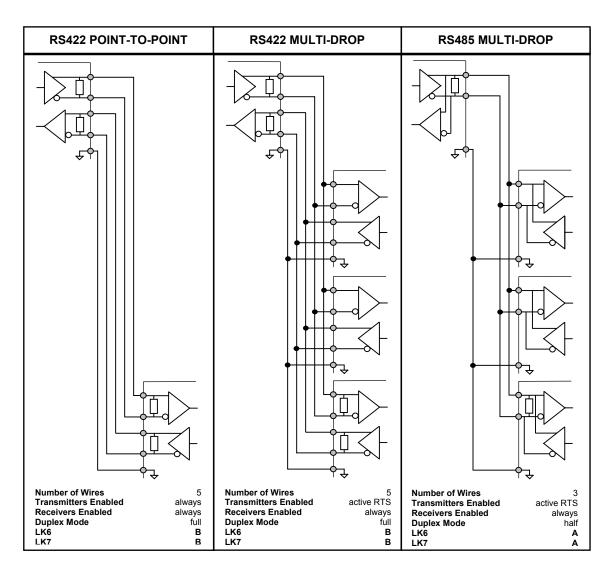

| Issue D | V2 Issue 4A | 25 <sup>th</sup> April 2007   | Updated to show RS422/485 termination resistor jumpers disconnected as default                                            |

© 2007 Arcom. Arcom is a subsidiary of Eurotech Group. <u>www.eurotech.com</u> For contact details, see page <u>101</u>.

Arcom operates a company-wide quality management system, which has been certified by the British Standards Institution (BSI) as compliant with ISO9001:2000

# Contents

| Introduction                                  | 4  |

|-----------------------------------------------|----|

| VIPER 'at a glance'                           | 5  |

| VIPER-Lite 'at a glance'                      | 6  |

| VIPER features                                | 7  |

| VIPER support products                        |    |

| Product handling and environmental compliance | 12 |

| Conventions                                   | 13 |

| Getting started                               | 15 |

| Using the VIPER                               |    |

| Detailed hardware description                 | 18 |

| VIPER block diagram                           | 18 |

| VIPER address map                             | 19 |

| Translations made by the MMU                  | 20 |

| PXA255 processor                              | 21 |

| PXA255 GPIO pin assignments                   |    |

| Real time clock                               |    |

| Watchdog timer                                |    |

| Memory                                        |    |

| Interrupt assignments                         |    |

| Flat panel display support                    |    |

| Audio                                         |    |

| General purpose I/O                           |    |

| USB host interface                            |    |

| USB client interface<br>10/100BaseTX Ethernet |    |

| Serial COMs ports                             |    |

| PC/104 interface                              |    |

| I <sup>2</sup> C                              |    |

| TPM                                           |    |

| JTAG and debug access                         |    |

| Power and power management                    |    |

| Power supplies                                |    |

| Power management                              |    |

| Connectors, LEDs, and jumpers                 |    |

| Connectors                                    |    |

| Status LEDs                                   |    |

| Jumpers                                       |    |

| Appendix A – Contacting Arcom                 |    |

| Appendix B – Specification                    |    |

| Appendix C – Mechanical diagram               |    |

| Appendix D – Reference information            |    |

| Appendix E – Acronyms and abbreviations       |    |

| Appendix E – Actoryms and abbreviations       |    |

|                                               |    |

| Index                                         |    |

# Introduction

The VIPER is an ultra low power, PC/104 compatible, single board computer available in two standard variants:

- VIPER, based on the 400MHz PXA255 XScale processor.

- VIPER-Lite, based on the 200MHz PXA255 XScale processor.

The PXA255 is an implementation of the Intel XScale micro architecture combined with a comprehensive set of integrated peripherals including: a flat panel graphics controller, interrupt controller, real time clock, and multiple serial ports. The VIPER board offers a wide range of features making it ideal for power sensitive embedded communications and multimedia applications.

Both of the standard variants are available in two memory configurations, as shown below:

| Variant    | Memory configuration | Details                                                                                 |

|------------|----------------------|-----------------------------------------------------------------------------------------|

| VIPER      | VIPER-M64-F32-V2-R6  | PXA255 400MHz microprocessor,<br>64MB SDRAM, 32MB FLASH.                                |

|            | VIPER-M64-F16-V2-R6  | PXA255 400MHz microprocessor,<br>64MB SDRAM, 16MB FLASH.                                |

| VIPER-Lite | VIPERL-M64-F32-V2-R6 | PXA255 200MHz microprocessor,<br>64MB SDRAM, 32MB FLASH, with reduced<br>functionality. |

|            | VIPERL-M64-F16-V2-R6 | PXA255 200MHz microprocessor,<br>64MB SDRAM, 16MB FLASH, with reduced<br>functionality. |

The VIPER and VIPER-Lite variants are also available in an industrial temperature range. Please contact our Sales team (see <u>Appendix A – Contacting Arcom</u>, page <u>101</u>) for availability.

The following features are *not* available on the standard VIPER-Lite configuration:

- PC/104 bus.

- USB host controller.

- Audio codec.

- COM4, COM5 serial ports.

- TPM (trusted platform module).

- SRAM (static random access memory).

Arcom can provide custom configurations (subject to a minimum order quantity) for the VIPER or the VIPER-Lite. Please contact our Sales team (see <u>Appendix A – Contacting</u> <u>Arcom</u>, page <u>101</u>) to discuss your requirements.

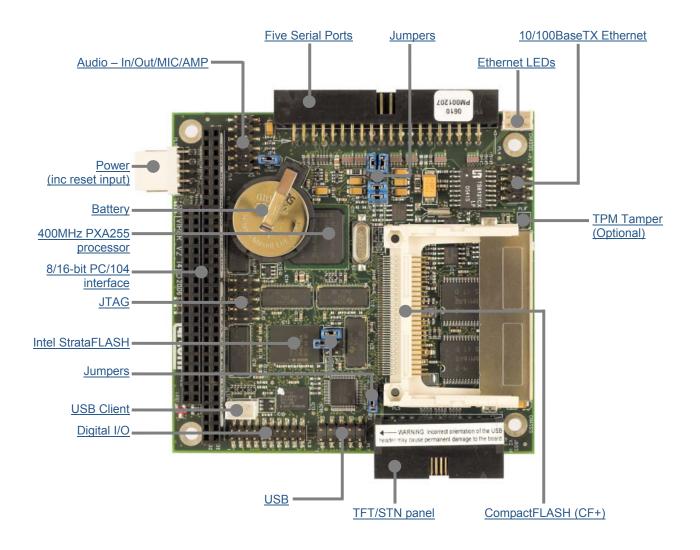

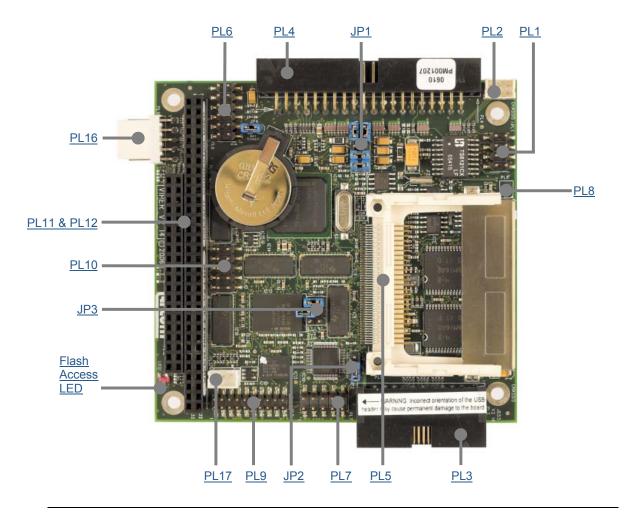

# VIPER 'at a glance'

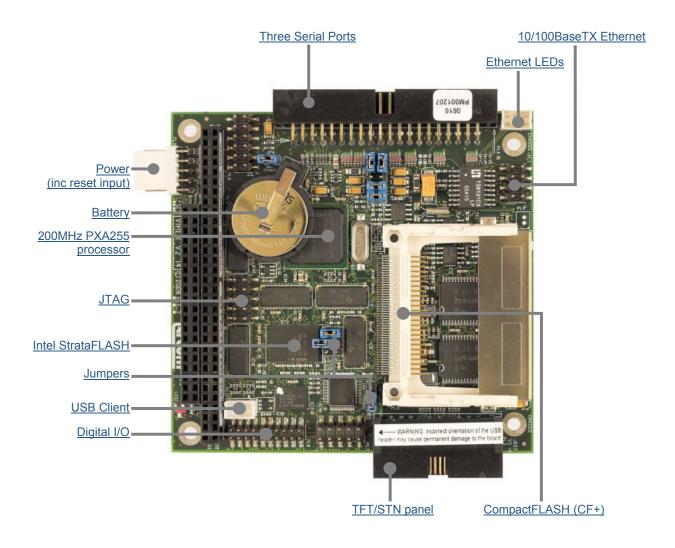

# VIPER-Lite 'at a glance'

# **VIPER** features

| Microprocessor            | PXA255 400MHz (VIPER) or 200MHz (VIPER-Lite) RISC processor.           |

|---------------------------|------------------------------------------------------------------------|

| Cache<br>•                | 32K data cache, 32K instruction cache, 2K mini data cache.             |

| System memory<br>•        | 64MB un-buffered 3.3V SDRAM.                                           |

| Silicon disk              |                                                                        |

| •                         | Up to 16/32MB Intel StrataFLASH (with FLASH access LED).               |

| •                         | 1MB bootloader FLASH EPROM (with FLASH access LED).                    |

| • 😥                       | 256KB SRAM (battery backed).                                           |

| •                         | Type I/II CompactFLASH (CF+) socket.                                   |

|                           |                                                                        |

| Video                     |                                                                        |

| •                         | TFT/STN (3.3V or 5V) flat panel graphics controller.                   |

| •                         | Up to 640X480 resolution.                                              |

| •                         | 8/16bpp.                                                               |

| •                         | Backlight control.                                                     |

| Audio                     |                                                                        |

| • 😥                       | National Semiconductor LM4529 AC'97 CODEC and LM4880 power amp.        |

| • 🕅                       | Line IN, line OUT, microphone, and 250mW per channel amplified output. |

| Serial ports <sup>1</sup> |                                                                        |

| •                         | 5 x 16550 compatible high-speed UARTs.                                 |

| •                         | 4 x RS232 and 1 x RS422/485 Interfaces.                                |

| •                         | 2 x channels with 128Byte Tx/Rx FIFO.                                  |

| USB host interface        |                                                                        |

|                           | Two USB 1.1 compliant interfaces.                                      |

|                           | Short circuit protection and 500mA current limit protection.           |

| •                         |                                                                        |

| USB client interface      |                                                                        |

| •                         | One USB 1.1 client interface.                                          |

|                           |                                                                        |

$<sup>^{1}</sup>$  COM4 (RS232) and COM5 (RS422/485) are not available on the VIPER-Lite.

| Network support       |        |                                                                                              |

|-----------------------|--------|----------------------------------------------------------------------------------------------|

|                       | ٠      | SMSC LAN91C111 10/100BaseTX Ethernet controller.                                             |

|                       | •      | One 10/100BaseTX NIC port.                                                                   |

| Trusted Platform Moo  | lule ( | (TPM) [optional]                                                                             |

| $\swarrow$            | •      | Atmel AT97SC3201 TPM security, with full TCG/TCPA V1.1b compatibility.                       |

| Ø                     | •      | Includes crypto accelerator capable of computing a 1024-bit RSA signature in 100ms.          |

| Real time clock (RTC) | )      |                                                                                              |

|                       | •      | Battery backed RTC.                                                                          |

|                       | •      | ± 1minute/month accuracy, at 25°C.                                                           |

| Watchdog              |        |                                                                                              |

|                       | •      | Adjustable timeout of 271ns to 19 minutes 25 seconds.                                        |

| General purpose I/O ( | 'GPIC  | )                                                                                            |

|                       | •      | 8 x 3.3V tolerant inputs (5V tolerant).                                                      |

|                       | •      | 8 x 3.3V outputs.                                                                            |

| User configuration    |        |                                                                                              |

|                       | •      | 1 user-configurable jumper.                                                                  |

| Expansion             |        |                                                                                              |

| (VI)                  | •      | PC/104 expansion bus - 8/16-bit ISA bus compatible interface.                                |

| JTAG port             |        |                                                                                              |

|                       | •      | Download data to FLASH memory.                                                               |

|                       | •      | Debug and connection to In-Circuit Emulator (ICE).                                           |

| Power                 |        | Typically 2W from a single 5V supply.                                                        |

|                       |        | Power management features allowing current requirements to be as low as                      |

|                       | -      | 49mA (245mW).                                                                                |

| Battery backup        |        |                                                                                              |

| 5 1                   | •      | Onboard battery holder containing a lithium-ion non-rechargeable CR2032, 3V, 220mAh battery. |

| Size                  |        |                                                                                              |

|                       | •      | PC/104 compatible footprint 3.8" x 3.6" (96mm x 91mm).                                       |

| Environmental         |        |                                                                                              |

|                       | •      | Operating temperature range:                                                                 |

|                       |        | - Commercial: -20°C (-4°F) to +70°C (+158°F)                                                 |

|                       |        | - Industrial: -40°C (-40°F) to +85°C (+185°F)                                                |

|                       | •      | RoHS directive (2002/95/EC) compliant                                                        |

|                       |        |                                                                                              |

# **VIPER** support products

The VIPER supports the following products:

### • VIPER-UPS (Uninterruptible Power Supply)

The VIPER-UPS serves as a 5V DC power supply and battery back up system for the VIPER. The UPS accepts between 10 – 36 VDC (10-25VAC) input and generates the +5V supply for the VIPER. In addition to this, it includes an intelligent battery charger/switch capable of using either the onboard 500mAHr NiMH battery or an external sealed lead acid rechargeable battery. For further details, see www.arcom.com/products/icp/pc104/processors/viper\_UPS.htm.

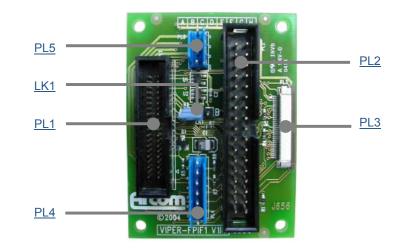

### • VIPER-FPIF1 (Flat Panel Interface)

The VIPER-FPIF1 is a simple board that enables easy connection between the VIPER and an LCD flat panel. See the section <u>VIPER-FPIF1 details</u>, page <u>38</u>, for further details. Contact Arcom (see <u>Appendix A – Contacting Arcom</u>, page <u>101</u>) for purchasing information.

### • ETHER-BREAKOUT

The ETHER-BREAKOUT is a simple board that converts the VIPER Ethernet 8-pin header and Ethernet LEDs 6-pin header to a standard RJ45 connector with LEDs. Contact Arcom (see <u>Appendix A – Contacting Arcom</u>, page <u>101</u>) for purchasing information.

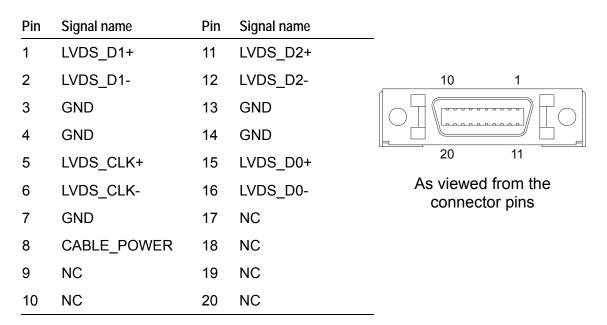

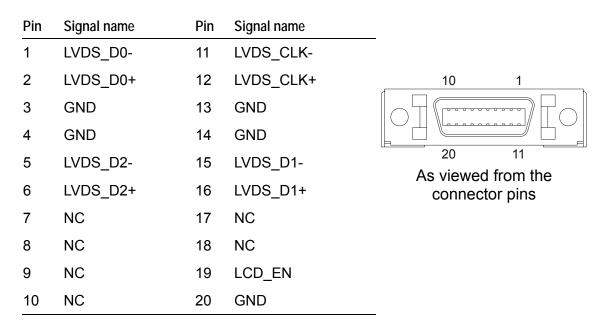

### • FPIF-LVDS-TX (Flat Panel Interface)

The FPIF-LVDS-TX enables LVDS displays to be connected to the VIPER. The FPIF-LVDS-TX in combination with the FPIF-LVDS-RX allows the VIPER to drive a TFT or STN LCD flat panel display up to 10 meters away. See the section <u>FPIF-LVDS-TX details</u>, page <u>43</u>, for further details. Contact Arcom (see <u>Appendix A – Contacting Arcom</u>, page <u>101</u>) for purchasing information.

### • FPIF-LVDS-RX (Flat Panel Interface)

The FPIF-LVDS-RX in combination with the FPIF-LVDS-TX allows the VIPER to drive a TFT or STN LCD flat panel display up to 10 meters away. See the section <u>FPIF-LVDS-RX details</u>, page <u>48</u>, for further details. Contact Arcom (see <u>Appendix A</u> <u>– Contacting Arcom</u>, page <u>101</u>) for purchasing information.

#### • FPIF-CRT (CRT Monitor or Analog FPD Interface)

The FPIF-CRT is a simple board that enables easy connection between the VIPER and a CRT Monitor or analog LCD flat panel. See the section <u>FPIF-CRT details</u>, page <u>53</u>, for further details. Contact Arcom (see <u>Appendix A – Contacting Arcom</u>, page <u>101</u>) for purchasing information.

#### • VIPER-I/O

VIPER-I/O is a low cost add-on I/O module for the PXA255 VIPER board. The board provides a variety of I/O features without the additional costs of a full PC/104 interface. The combination of the VIPER and VIPER–I/O is suited to control and monitoring applications that require a limited number of isolated inputs and outputs. See the section <u>VIPER-I/O</u>, page <u>59</u>, for further details. Contact Arcom (see <u>Appendix A – Contacting Arcom</u>, page <u>101</u>) for purchasing information.

#### CYCLOPS

The CYCLOPS is a rugged VIPER display terminal. The enclosure can be configured to suit a complete range of embedded applications with LCD display and touchscreen.

#### VIPER-ICE (Industrial Compact Enclosure) development kits

The VIPER-ICE is a simple low cost aluminum enclosure, which provides easy connection to all on board features. The enclosure includes the VIPER-UPS and optionally a color Q-VGA (320x240) TFT flat panel display and analog touchscreen. The VIPER-ICE is available with a wide range of development kits. These are described in the section <u>Development kits available for the VIPER</u>, page <u>10</u>. For further details, see <u>www.arcom.com/development-kits.htm</u>.

#### Development kits available for the VIPER

- Windows CE/CE 5.0 development kit Features of this kit are:

- 400MHz PXA255 processor with 64MB DRAM & 32MB Flash memory.

- Pre-configured build of Windows CE 5.0 tailored specifically for the VIPER, preloaded into the 32MB Flash.

- Windows CE 5.0 Platform SDK for VIPER.

- Rugged enclosure with <u>NEC Q-VGA TFT color 5.5 and display</u> and analog touchscreen.

- Uninterruptible power supply (<u>VIPER-UPS</u>) to allow VIPER system to continue to operate without main power. Example code is supplied to handle the power loss warning and battery backup control features.

- 24V power supply module with power cords for US, UK, and European power sockets.

- Arcom Development Kit CD containing Windows CE 5.0 operating system image, sample code, Technical Manual, and datasheets.

- Quickstart manual.

### Embedded Linux development kit

Features of this kit are:

- 400MHz PXA255 processor with 64MB DRAM & 32MB Flash memory.

- Pre-configured build of Arcom's Embedded Linux, tailored specifically for the VIPER, pre-loaded into the 32MB Flash.

- 2.6-based Linux kernel release, GNU C library.

- Compressed Journaling Flash File System (JFFS2) offering high reliability and recovery from power interruptions.

- Rugged enclosure with optional <u>NEC Q-VGA TFT color display</u> and analog touchscreen.

- Uninterruptible power supply (<u>VIPER-UPS</u>) to allow VIPER system to continue to operate without main power.

- 24V power supply module with power cords for US, UK, and European power sockets.

- Optional high performance IBM J9 VM.

- Quickstart tutorial guide.

# • Wind River VxWorks 5.5 development kit

Features of this kit are:

- 400MHz PXA255 processor with 64MB DRAM & 32MB Flash memory.

- VxWorks BSP for Tornado 2.2.1/VxWorks 5.5.1/Wind ML 3.0.2.

- Pre-configured build of VxWorks, tailored specifically for the VIPER, pre-loaded into the 32MB Flash.

- Rugged enclosure with optional <u>NEC Q-VGA TFT color display</u> and analog touchscreen.

- Uninterruptible power supply (<u>VIPER-UPS</u>) to allow VIPER system to continue to operate without main power.

- 24V power supply module with power cords for US, UK, and European power sockets.

### Entry level development kits for VIPER or VIPER-Lite

The following entry level development kits are available:

### • Windows CE / CE 5.0 development kit

Features of this kit for VIPER or VIPER-Lite are:

- 400MHz (VIPER) or 200MHz (VIPER-Lite) PXA255 processor with 64MB DRAM & 32MB Flash memory.

- Pre-configured build of Windows CE 5.0 tailored specifically for the VIPER, preloaded into the 32MB Flash.

- +5V PSU.

- All cables for immediate operation and download.

- Development kit documentation.

- Optional VIPER-I/O module.

#### Embedded Linux development kit

Features of this kit for VIPER or VIPER-Lite are:

- 400MHz (VIPER) or 200MHz (VIPER-Lite) PXA255 processor with 64MB DRAM & 32MB Flash memory.

- Pre-configured build of Arcom's Embedded Linux, tailored specifically for the VIPER, pre-loaded into the 32MB Flash.

- +5V PSU.

- All cables for immediate operation and download.

- Development kit documentation.

- Optional VIPER-I/O module.

# Product handling and environmental compliance

#### Anti-static handling

This board contains CMOS devices that could be damaged in the event of static electricity discharged through them. At all times, please observe anti-static precautions when handling the board. This includes storing the board in appropriate anti-static packaging and wearing a wrist strap when handling the board.

### Packaging

Please ensure that should a board need to be returned to Arcom, it is adequately packed, preferably in the original packing material.

#### Electromagnetic compatibility (EMC)

The VIPER is classified as a component with regard to the European Community EMC regulations and it is the users responsibility to ensure that systems using the board are compliant with the appropriate EMC standards.

#### **RoHS** Compliance

The European RoHS Directive (Restriction on the use of certain Hazardous Substances – Directive 2002/95/EC) limits the amount of 6 specific substances within the composition of the product. The VIPER, VIPER-Lite, and associated accessory products are available as RoHS-6 compliant options and are identified by a -R6 suffix in the product order code. A full RoHS Compliance Materials Declaration Form is included in <u>Appendix F – RoHS-6 Compliance - Materials Declaration Form</u>, page <u>108</u>. Further information about RoHS compliance is available on the Arcom web site – <u>http://www.arcom.com/RoHS and WEEE/</u>.

# Conventions

## Symbols

The following symbols are used in this guide:

| Symbol | Explanation |

|--------|-------------|

| Symbol |             |

Note - information that requires your attention.

Tip - a handy hint that may provide a useful alternative or save time.

Caution - proceeding with a course of action may damage your equipment or result in loss of data.

Indicates that a feature is <u>not</u> available on the standard VIPER-Lite configuration. Arcom can provide custom configurations (subject to a minimum order quantity) for the VIPER-Lite populated with this feature. Please contact our Sales team (see <u>Appendix A – Contacting Arcom</u>, page <u>101</u>) to discuss your requirements.

Jumper is fitted.

Jumper is not fitted.

Jumper fitted on pins 1-2.

Jumper fitted on pins 2-3.

# Tables

With tables such as that shown below, the white cells show information relevant to the subject being discussed. Grey cells are not relevant in the current context.

| Byte lane | Most Significant Byte |    |    |    |    |    | Least Significant Byte |   |   |   |   |   |   |        |              |       |

|-----------|-----------------------|----|----|----|----|----|------------------------|---|---|---|---|---|---|--------|--------------|-------|

| Bit       | 15                    | 14 | 13 | 12 | 11 | 10 | 9                      | 8 | 7 | 6 | 5 | 4 | 3 | 2      | 1            | 0     |

| Field     | -                     | -  | -  | -  | -  | -  | -                      | - | - | - | - | - | - | RETRIG | AUTO_<br>CLR | R_DIS |

| Reset     | Х                     | Х  | Х  | Х  | Х  | Х  | Х                      | Х | 0 | 0 | 0 | 0 | 0 | 0      | 0            | 0     |

|           |                       |    |    |    |    |    |                        |   |   |   |   |   |   |        |              |       |

# Getting started

Depending on the development kit purchased, a Quickstart Manual is provided for Windows CE, embedded Linux, or VxWorks to enable users to set-up and start using the board. Please read the relevant manual and follow the steps defining the set-up of the board. Once you have completed this task you will have a working VIPER system and can start adding further peripherals enabling development to begin.

This section provides a guide to setting up and using of some of the features of the VIPER. For more detailed information on any aspect of the board see <u>Detailed</u> <u>hardware description</u>, page <u>18</u>.

# Using the VIPER

### Using the CompactFLASH<sup>™</sup> socket

The VIPER is fitted with a Type I/II CompactFLASH socket mounted on the topside of the board. The socket is connected to Slot 0 of the PXA255 PC card interface. It supports 3.3V Type I and II CompactFLASH cards for both memory and IO. The VIPER supports hot swap changeover of the cards and notification of card insertion.

RedBoot supports ATA type CompactFlash cards. Files can be read providing the card is formatted with an EXT2 file system. Eboot cannot boot from CompactFlash.

5V CompactFLASH is not supported.

The CompactFLASH card can only be inserted one way into the socket. The correct orientation is for the top of the card, i.e. with the normal printed side face down to the PCB.

### Using the serial interfaces (RS232/422/485)

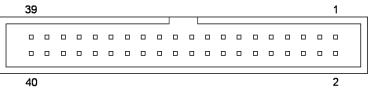

The five serial port interfaces on the VIPER are fully 16550 compatible. Connection to the serial ports is made via a 40-way boxed header. The pin assignment of this header has been arranged to enable 9-way IDC D-Sub plugs to be connected directly to the cable. See the section  $\underline{PL4} - \underline{COMS}$  ports, page <u>89</u>, for pin assignment and connector details.

A suitable cable for COM1 is provided as part of the development kit. The D-Sub connector on this cable is compatible with the standard 9-way connector on a desktop computer.

COM4 (RS232) and COM5 (RS422/485) are <u>not</u> available on the standard

VIPER-Lite configuration. Arcom can provide custom configurations (subject to a minimum order quantity) for the VIPER-Lite populated with this feature. Please contact our Sales team (see <u>Appendix A – Contacting Arcom</u>, page <u>101</u>) to discuss your requirements.

#### Using the audio features

There are four audio interfaces supported on the VIPER: amp out, line out, line in, and microphone. The line in, line out, and amp interfaces support stereo signals and the microphone provides a mono input. The amplified output is suitable for driving an  $8\Omega$  load with a maximum power output of 250mW per channel. Connections are routed to PL6 - see the sections Audio (page 56) and PL6 – Audio connector (page 91) for further details.

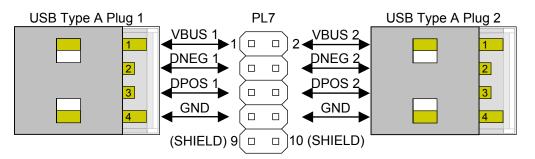

#### Using the USB host

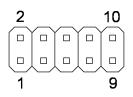

The standard USB connector is a 4-way socket, which provides power and data signals to the USB peripheral. The 10-way header PL7 has been designed to be compatible with PC expansion brackets that support two USB sockets. See the sections <u>USB host</u> interface (page <u>60</u>) and <u>PL7 – USB connector</u> (page <u>91</u>) for further details.

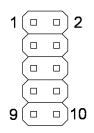

#### Using the USB client

The VIPER board can be used as USB client and connected to a PC via a USB cable. The USB cable should be plugged into PL17 header. See the sections <u>USB client</u> <u>interface</u> (page <u>61</u>) and <u>PL17 – USB client connector</u> (page <u>95</u>) for further details.

#### Using the Ethernet interface

The SMSC LAN91C111 10/100BaseTX Ethernet controller is configured by the RedBoot bootloader for embedded Linux or VxWorks, and by Eboot for Windows CE.

Connection is made via connector PL1. A second connector PL2 provides activity and link status outputs for control LEDs. See the sections 10/100BaseTX Ethernet (page 62), PL1 – 10/100BaseTX Ethernet connector (page 87) and PL2 – Ethernet status LEDs connector (page 87) for further details.

The Ethernet port may be connected to an ETHER-BREAKOUT module to provide a standard RJ45 port connector, see section <u>Ethernet breakout board</u>, page <u>62</u> for further details.

#### Using the PC/104 expansion bus

PC/104 modules can be used with the VIPER to add extra functionality to the system. This interface supports 8/16 bit ISA bus style peripherals.

Arcom has a wide range of PC/104 modules, which are compatible with the VIPER. These include modules for digital I/O, analog I/O, motion control, CAN bus, serial interfaces, etc. Please contact the Arcom sales team if a particular interface you require does not appear to be available as these modules are in continuous development. Contact details are provided in <u>Appendix A – Contacting Arcom</u>, page <u>101</u>.

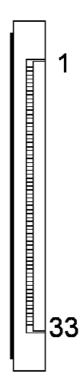

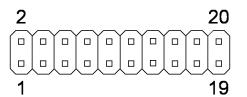

In order to use a PC/104 board with the VIPER it should be plugged into PL11 for 8-bit cards and PL11/PL12 for 8/16-bit cards. See the sections PC/104 interface (page 67) and PL11 & PL12 - PC/104 connectors (page 94) for further details.

The ISA interface on the VIPER does not support DMA or shared interrupts. See the section <u>Interrupt assignments</u>, page <u>30</u>, for details about PC/104 interrupt use.

The VIPER provides +5V to a PC/104 add-on board via the PL11 and PL12 connectors. If a PC/104 add-on board requires a +12V supply, then +12V must be supplied to the VIPER power connector PL16 pin 4. If -12V or -5V are required, these must be supplied directly to the PC/104 add-on board.

The VIPER is available with non-stack through connectors by special order. Contact Arcom (see <u>Appendix A – Contacting Arcom</u>, page <u>101</u>, for more details.

# **Detailed hardware description**

The following section provides a detailed description of the functions provided by the VIPER. This information may be required during development after you have started adding extra peripherals or are starting to use some of the embedded features.

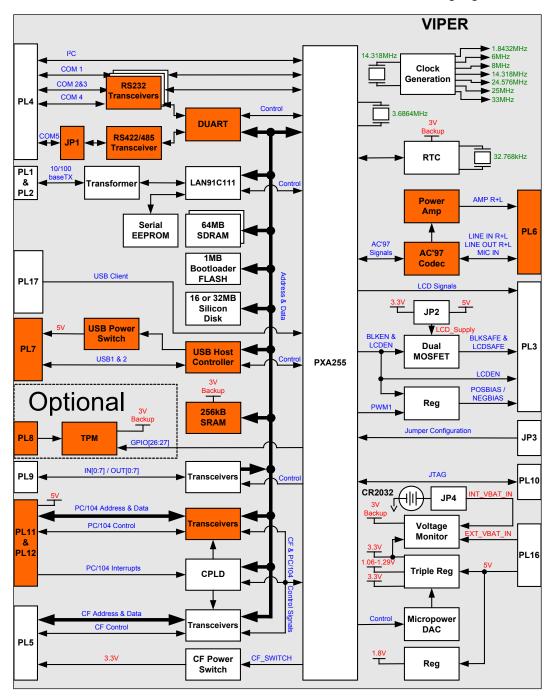

# VIPER block diagram

The diagram below illustrates the functional organization of the VIPER PC/104 SBC. Functions that are not available with the standard VIPER-Lite are highlighted in orange.

# VIPER address map

|              | PXA255         |                         | Puc/register          |                                           |

|--------------|----------------|-------------------------|-----------------------|-------------------------------------------|

|              | chip<br>select | Physical address        | Bus/register<br>width | Description                               |

|              | -              | 0xA4000000 – 0xFFFFFFF  | -                     | Reserved                                  |

|              | SDCS0          | 0xA0000000 – 0xA3FFFFC  | 32-bit                | SDRAM, IC2&3                              |

|              | -              | 0x4C000000 – 0x9FFFFFF  | -                     | Reserved                                  |

|              | NA             | 0x48000000 – 0x4BFFFFFF | 32-bit                | Memory Control Registers <sup>1</sup>     |

|              | NA             | 0x44000000 – 0x47FFFFFF | 32-bit                | LCD Control Registers <sup>1</sup>        |

|              | NA             | 0x40000000 – 0x43FFFFFF | 32-bit                | PXA255 Peripherals <sup>1</sup>           |

|              | -              | 0x3C200400 – 0x3FFFFFFF | -                     | Reserved                                  |

| Ø            | NA             | 0x3C000000 – 0x3C1FFFFF | 8/16-bit              | PC/104 Memory Space                       |

|              | -              | 0x30000400 – 0x3BFFFFFF | -                     | Reserved                                  |

| $\swarrow$   | NA             | 0x30000000 – 0x300003FF | 8/16-bit              | PC/104 I/O Space                          |

|              | NA             | 0x20000000 – 0x2FFFFFFF | 32-bit                | CompactFLASH, PL5                         |

|              | -              | 0x14880000 – 0x1FFFFFF  | -                     | Reserved                                  |

| Ø            | CS5            | 0x14800000 – 0x1487FFFF | 16-bit                | SRAM (see page <u>28</u> )                |

|              | -              | 0x14500002 – 0x47FFFFFF | -                     | Reserved                                  |

|              | CS5            | 0x14500000 – 0x14500001 | 16-bit                | General purpose I/O (see page <u>57</u> ) |

|              | -              | 0x14300020 – 0x144FFFFF | -                     | Reserved                                  |

| <b>V</b>     | CS5            | 0x14300010 – 0x1430001F | 16-bit                | COM4 (see page <u>65</u> )                |

| <b>V</b>     | CS5            | 0x14300000 – 0x1430000F | 16-bit                | COM5 (see page <u>65</u> )                |

| _            | -              | 0x14100006 – 0x142FFFFF | -                     | Reserved                                  |

| $\checkmark$ | CS5            | 0x14100004 – 0x14100005 | 16-bit                | PC104I2 Register (see page <u>31</u> )    |

| $\checkmark$ | CS5            | 0x14100002 - 0x14100003 | 16-bit                | ICR Register (see page <u>31</u> )        |

| $\checkmark$ | CS5            | 0x14100000 - 0x14100001 | 16-bit                | PC104I1 Register (see page 31)            |

|              | -              | 0x10000004 – 0x140FFFFF | -                     | Reserved                                  |

|              | CS4            | 0x1000000 – 0x100007FF  | 32-bit                | Ethernet Data port                        |

|              | -              | 0x0C000004 – 0x0FFFFFF  | -                     | Reserved                                  |

| Ø            | CS3            | 0x0C000000 - 0x0C000002 | 16-bit                | USB Host Controller                       |

|              | -              | 0x08000310 – 0x0BFFFFFF | -                     | Reserved                                  |

|              | CS2            | 0x08000300 - 0x0800030E | 16-bit                | Ethernet I/O Space                        |

|              | -              | 0x06000000 – 0x080002FF | -                     | Reserved                                  |

|              | CS1            | 0x04000000 – 0x05FFFFFE | 16-bit                | FLASH Memory / Silicon Disk               |

|              | -              | 0x00100000 – 0x03FFFFFF | -                     | Reserved                                  |

|              | CS0            | 0x00000000 – 0x000FFFFE | 16-bit                | Bootloader FLASH                          |

Details of the internal registers are in the Intel Developer Manual on the Development Kit CD.

1

# Translations made by the MMU

For details of translations made by the MMU by Redboot for embedded Linux, please refer to the VIPER Embedded Linux AEL Technical Manual.

For details of translations made by the MMU by Redboot for VxWorks, please refer to the VIPER VxWorks Quickstart and Technical Manual.

For details of translations made by the MMU for Windows CE, please check the Windows CE documentation for more information about memory mapping. One source of this information is on the MSDN web site (<u>www.msdn.microsoft.com</u>) under *Windows CE Memory Architecture*.

### PXA255 processor

The PXA255 is a low power ARM (version 5TE) instruction set compliant RISC processor. The PXA255 does not include a floating-point unit. The device does, however, contain a DSP co-processor to enhance multimedia applications.

The VIPER is fitted with a 400MHz PXA255 variant and the VIPER-Lite is fitted with a 200MHz PXA255 variant. The clock source for these is a 3.6864 MHz clock, which generates all the high-speed clocks within the device. The default run mode frequency is 400MHz for the VIPER and 200MHz for the VIPER-Lite. Currently embedded Linux and VxWorks supports changing the operating frequency and Windows CE will provide support shortly. Please refer to the relevant operating system technical manual to select an alternative operating frequency.

The processor has two supply inputs: I/O and core generated on the VIPER from the main +5V supply input. The I/O supply is powered from +3.3V, and the core is powered from a +1.06 to +1.3V adjustable supply. See the section <u>Processor power</u> <u>management</u>, page <u>81</u>, for operation details.

The PXA255 has an integrated memory and CompactFlash controller with 100 MHz memory bus, 32KB data and 32KB instruction caches, and 2KB mini data cache for streaming data.

The PXA255 provides up to 85 GPIO pins, many of which have been configured for alternative functions like the AC'97 and PC card/CompactFLASH interfaces. Details of these pin configurations are provided in the section <u>PXA255 GPIO pin assignments</u>, page <u>22</u>.

The PXA255 also has the following features that can be used on the VIPER:

- Peripheral Control Module:

- 16 channel configurable DMA controller (for internal use only).

- Integrated LCD controller with unique DMA for fast color screen support.

- Serial ports including AC'97, 3 UARTs, and enhanced USB end point interface.

- System Control Module:

- General-purpose interruptible I/O ports.

- Real time clock.

- Watchdog.

- Interval timers.

- Power management controller.

- Interrupt controller.

- Reset controller.

- Two on-chip oscillators.

The PXA255 processor is packaged in a 256-pin PBGA, which is attached to the board during the assembly process.

The PXA255 processor is a low power device and does not require a heat sink for temperatures up to 70°C (85°C for the industrial variant).

# PXA255 GPIO pin assignments

The following table summarizes the use of the 85 PXA255 GPIO pins, their direction, alternate function, and active level.

For embedded Linux the GPIO pins are setup by Redboot. Under VxWorks and Windows CE, they are setup by the OS and not by the bootloader.

|   | Key<br>AF<br>Dir<br>Act<br>Sle | ive       | Alternate fur<br>Pin direction<br>Function act<br>Pin state dur | ring sleep). |                |       |                                          |                                                                     |

|---|--------------------------------|-----------|-----------------------------------------------------------------|--------------|----------------|-------|------------------------------------------|---------------------------------------------------------------------|

|   |                                | Pio<br>Af | Signal name                                                     | Dir          | Active         | Sleep | Function                                 | See section                                                         |

|   | 0                              | 0         | ETHER_INT                                                       | Input        | _              | Input | Ethernet Interrupt                       |                                                                     |

| Ø | 1                              | 0         | PC/104_IRQ                                                      | Input        | See            | Input | CPLD Interrupt                           |                                                                     |

|   | -                              |           |                                                                 |              | page <u>30</u> |       |                                          | Interrupt assignments<br>(page <u>30</u> )                          |

|   | 2                              | 0         | USB_IRQ                                                         | Input        |                | Input | USB Interrupt                            | (pugo <u>oo</u> )                                                   |

|   | 3                              | 0         | UART_INT1                                                       | Input        |                | Input | COM 5 Interrupt                          |                                                                     |

|   | 4                              | 0         | UART_INT2                                                       | Input        | _ <b>_</b>     | Input | COM 4 Interrupt                          |                                                                     |

|   | 5                              | 0         | Reserved                                                        | Input        | NA             | Input | Reserved                                 | Reserved – LK2 (page <u>98</u> )                                    |

|   | 6                              | 0         | PSU_DATA                                                        | Output       | NA             | 0     | Microprocessor Core<br>Voltage DAC Data  | Processor power<br>management (page <u>81</u> )                     |

|   | 7                              | 0         | USER_CONFIG1                                                    | Input        | NA             | Input | User Config 1, Jumper<br>LK3             | <u>User configurable jumper 1</u><br><u>– LK3</u> (page <u>98</u> ) |

|   | 8                              | 0         | CF_RDY                                                          | Input        | NA             | Input | CompactFLASH<br>Ready/nBusy              | Interrupt assignments, (page 30 and CompactFLASH page 28)           |

|   | 9                              | 0         | BLKEN                                                           | Output       | High           | 0     | LCD Backlight Enable                     | LCD backlight enable (page <u>37</u> )                              |

|   | 10                             | 0         | LCDEN                                                           | Output       | High           | 0     | LCD Logic Supply<br>Enable               | LCD logic supply enable (page <u>37</u> )                           |

|   | 11                             | 0         | PSU_CLK                                                         | Output       | _              | 0     | Microprocessor Core<br>Voltage DAC Clock | Processor power<br>management (page 81)                             |

|   | 12                             | 0         | SHDN                                                            | Output       | High           | 1     | COM 1, 2, 3 & 4 UART<br>Shutdown         | UART power management<br>(page <u>83</u> )                          |

|   | 13                             | 0         | USB_WAKEUP                                                      | Output       | High           | 0     | Wake Up USB Host<br>from suspend         | USB power management<br>(page <u>83</u> )                           |

|   | . <u> </u>                     |           |                                                                 |              |                |       |                                          | continued                                                           |

| N <u>o</u> | AF | Signal name      | Dir    | Active                       | Sleep | Function                                             | See section                                                                      |

|------------|----|------------------|--------|------------------------------|-------|------------------------------------------------------|----------------------------------------------------------------------------------|

| 14         | 0  | FLASH_<br>STATUS | Input  | NA                           | Input | Bootloader FLASH<br>Status,<br>Ready / nBusy         | Interrupt assignments (page<br>30) and FLASH<br>memory/silicon disk (page<br>27) |

| 15         | 2  | CS1              | Output | Low                          | Hi-Z  | Chip Select 1                                        | <u>VIPER address map</u><br>(page <u>19</u> )                                    |

| 16         | 2  | PWM0             | Output | See<br>inverter<br>datasheet | 0     | Backlight Brightness<br>On/Off or variable if<br>PWM | LCD backlight brightness<br>control (page <u>37</u> )                            |

| 17         | 2  | PWM1             | Output | NA                           | 0     | STN Bias                                             | STN BIAS voltage (page 38                                                        |

| 18         | 1  | ARDY             | Input  | Low                          | Input | 10/100 Ethernet PHY<br>Ready                         | -                                                                                |

| 19         | 0  | PSU_nCS_LD       | Output | Low                          | 0     | Microprocessor Core<br>Voltage DAC Chip<br>Select    | Processor power<br>management (page <u>81</u> )                                  |

| 20         | 0  | OUT0             |        |                              |       |                                                      |                                                                                  |

| 21         | 0  | OUT1             |        |                              |       |                                                      |                                                                                  |

| 22         | 0  | OUT2             |        |                              |       |                                                      |                                                                                  |

| 23         | 0  | OUT3             | Output | User                         | 0     | User Config                                          | General purpose I/O                                                              |

| 24         | 0  | OUT4             | Ουιρυι | Config                       |       | User Coning                                          | (page <u>57</u> )                                                                |

| 25         | 0  | OUT5             |        |                              |       |                                                      |                                                                                  |

| 26         | 0  | OUT6             |        |                              |       |                                                      |                                                                                  |

| 27         | 0  | OUT7             |        |                              |       |                                                      |                                                                                  |

| 28         | 1  | AC97_BITCLK      | Input  | _ <b>_</b>                   | Input | BITCLK                                               |                                                                                  |

| 29         | 1  | AC97_IN          | Input  | NA                           | Input | SDATA_IN0                                            |                                                                                  |

| 30         | 2  | AC97_OUT         | Output | NA                           | 0     | SDATA_OUT                                            | -                                                                                |

| 31         | 2  | AC97_SYNC        | Output | _                            | 0     | SYNC                                                 |                                                                                  |

| 32         | 0  | CF_DETECT        | Input  | ₹_                           | Input | CF Detection                                         | Interrupt assignments (page 30) and <u>CompactFLASH</u> (page 28)                |

| 33         | 2  | CPLDCS           | Output | Low                          | Hi-Z  | Chip Select 5                                        | <u>VIPER address map</u> , (page <u>19</u> )                                     |

|            |    |                  |        |                              |       |                                                      | continued.                                                                       |

| GF<br>N <u>o</u> | Pio<br>Af | Signal name | Dir    | Active | Sleep | Function                                                | See section                                      |

|------------------|-----------|-------------|--------|--------|-------|---------------------------------------------------------|--------------------------------------------------|

| 34               | 1         | RXD1        | Input  | NA     | Input | COM1 Receive Data                                       |                                                  |

| 35               | 1         | CTS1        | Input  | NA     | Input | COM1 Clear To Send                                      |                                                  |

| 36               | 1         | DCD1        | Input  | NA     | Input | COM1 Data Carrier<br>Detect                             |                                                  |

| 37               | 1         | DSR1        | Input  | NA     | Input | COM1 Data Sender<br>Ready                               |                                                  |

| 38               | 1         | RI1         | Input  | NA     | Input | COM1 Ring Indicator                                     |                                                  |

| 39               | 2         | TXD1        | Output | NA     | 0     | COM1 Transmit Data                                      |                                                  |

| 40               | 2         | DTR1        | Output | NA     | 0     | COM1 Data Terminal<br>Ready                             | Serial COMs ports (page 64) and PL4 – COMS ports |

| 41               | 2         | RTS1        | Output | NA     | 0     | COM1 Request To<br>Send                                 | (page <u>89</u> ).                               |

| 42               | 1         | RXD2        | Input  | NA     | Input | COM2 Receive Data                                       |                                                  |

| 43               | 2         | TXD2        | Output | NA     | 0     | COM2 Transmit Data                                      |                                                  |

| 44               | 1         | CTS2        | Input  | NA     | Input | COM2 Clear To Send                                      |                                                  |

| 45               | 2         | RTS2        | Output | NA     | 0     | COM2 Request To<br>Send                                 |                                                  |

| 46               | 2         | RXD3        | Input  | NA     | Input | COM3 Receive Data                                       |                                                  |

| 47               | 1         | TXD3        | Output | NA     | 0     | COM3 Transmit Data                                      |                                                  |

| 48               | 2         | CB_POE      | Output | Low    | 1     | Socket 0 & 1 Output<br>Enable                           |                                                  |

| 49               | 2         | CB_PWE      | Output | Low    | 1     | Socket 0 & 1 Write<br>Enable                            |                                                  |

| 50               | 2         | CB_PIOR     | Output | Low    | 1     | Socket 0 & 1 I/O Read                                   | _                                                |

| 51               | 2         | CB_PIOW     | Output | Low    | 1     | Socket 0 & 1 I/O Write                                  |                                                  |

| 52               | 2         | CB_PCE1     | Output | Low    | 1     | Socket 0 & 1 Low Byte<br>Enable                         |                                                  |

| 53               | 2         | CB_PCE2     | Output | Low    | 1     | Socket 0 & 1 High<br>Byte Enable                        |                                                  |

| 54               | 2         | CB_PKTSEL   | Output | NA     | 1     | PSKTSEL 0 = Socket<br>0 Select / 1 = Socket 1<br>Select | -                                                |

| 55               | 2         | CB_PREG     | Output | Low    | 1     | PREG                                                    | -                                                |

| 56               | 1         | CB_PWAIT    | Input  | Low    | Input | PWAIT                                                   | _                                                |

| 57               | 1         | CB_PIOIS16  | Input  | Low    | Input | IOIS16                                                  | -                                                |

|                  |           |             |        |        |       |                                                         | continued                                        |

|    | Pio<br>Af | Signal name | Dir                | Active | Sleep | Function                                        | See section                                                                                            |

|----|-----------|-------------|--------------------|--------|-------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| 58 | 2         | LCD_D0      | Output             | NA     | 0     | LCD Data Bit 0                                  |                                                                                                        |

| 59 | 2         | LCD_D1      | Output             | NA     | 0     | LCD Data Bit 1                                  |                                                                                                        |

| 60 | 2         | LCD_D2      | Output             | NA     | 0     | LCD Data Bit 2                                  |                                                                                                        |

| 61 | 2         | LCD_D3      | Output             | NA     | 0     | LCD Data Bit 3                                  |                                                                                                        |

| 62 | 2         | LCD_D4      | Output             | NA     | 0     | LCD Data Bit 4                                  |                                                                                                        |

| 63 | 2         | LCD_D5      | Output             | NA     | 0     | LCD Data Bit 5                                  |                                                                                                        |

| 64 | 2         | LCD_D6      | Output             | NA     | 0     | LCD Data Bit 6                                  |                                                                                                        |

| 65 | 2         | LCD_D7      | Output             | NA     | 0     | LCD Data Bit 7                                  |                                                                                                        |

| 66 | 2         | LCD_D8      | Output             | NA     | 0     | LCD Data Bit 8                                  |                                                                                                        |

| 67 | 2         | LCD_D9      | Output             | NA     | 0     | LCD Data Bit 9                                  |                                                                                                        |

| 68 | 2         | LCD_D10     | Output             | NA     | 0     | LCD Data Bit 10                                 | Flat panel display support                                                                             |

| 69 | 2         | LCD_D11     | Output             | NA     | 0     | LCD Data Bit 11                                 | (page <u>34</u> ) and <u>PL3 – LCD</u><br>connector (page <u>88</u> )                                  |

| 70 | 2         | LCD_D12     | Output             | NA     | 0     | LCD Data Bit 12                                 | <u> </u>                                                                                               |

| 71 | 2         | LCD_D13     | Output             | NA     | 0     | LCD Data Bit 13                                 |                                                                                                        |

| 72 | 2         | LCD_D14     | Output             | NA     | 0     | LCD Data Bit 14                                 |                                                                                                        |

| 73 | 2         | LCD_D15     | Output             | NA     | 0     | LCD Data Bit 15                                 |                                                                                                        |

| 74 | 2         | LCD_FCLK    | Output             | NA     | 0     | LCD Frame Clock (STN)<br>Vertical Sync (TFT)    |                                                                                                        |

| 75 | 2         | LCD_LCLK    | Output             | NA     | 0     | LCD Line Clock (STN) /<br>Horizontal Sync (TFT) |                                                                                                        |

| 76 | 2         | LCD_PCLK    | Output             | NA     | 0     | LCD Pixel Clock<br>(STN) / Clock (TFT)          |                                                                                                        |

| 77 | 2         | LCD_BIAS    | Output             | NA     | 0     | LCD Bias (STN) / Date<br>Enable (TFT)           |                                                                                                        |

| 78 | 2         | ETHERCS2    | Output             | Low    | Hi-Z  | Chip Select 2                                   |                                                                                                        |

| 79 | 2         | USBCS       | Output             | Low    | Hi-Z  | Chip Select 3                                   | <u>VIPER address map</u> (page<br><u>19</u> )                                                          |

| 80 | 2         | ETHERCS1    | Output             | Low    | Hi-Z  | Chip Select 4                                   | /                                                                                                      |

| 81 | 0         | SDRAM       | Input              | NA     | Input | SDRAM Size<br>Detection 0 = 64MB,<br>1 = 16MB   | -                                                                                                      |

| 82 | 0         | CF_SWITCH   | Output             | High   | 0     | CompactFLASH<br>Power Switch Enable             | CompactFLASH (page <u>28</u> )<br>and <u>CompactFLASH power</u><br><u>management</u> (page <u>83</u> ) |

| 83 | 0         | RTC_IO      | Bidirec-<br>tional | NA     | 0     | RTC Data                                        | Real time clock (page 26)                                                                              |

| 84 | 0         | RTC_CLK     | Output             | ₹_     | 0     | RTC Clock                                       |                                                                                                        |

# Real time clock

There are two RTCs on the VIPER. Under embedded Linux and VxWorks the internal RTC of the PXA255 should only be used for power management events, and an external Dallas DS1338 RTC should be used to keep the time and date. Under Windows CE the time and date stamps are copied from the external RTC to the internal RTC of the PXA255, to run the RTC internally.

The accuracy of the DS1338 RTC is based on the operation of the 32.768KHz watch crystal. Its calibration tolerance is ±20ppm, which provides an accuracy of +/-1 minute per month if the board is in an ambient environment of +25°C. When the board is operated outside this temperature then the accuracy may be degraded by -0.035ppm/ $^{\circ}C^{2} \pm 10\%$  typical. The watch crystal's accuracy will age by ±3ppm max in the first year, then ±1ppm max in the year after, and logarithmically decreasing in subsequent years.

The following PXA255 GPIO pins are used to emulate the I<sup>2</sup>C interface to the DS1338 RTC:

| PXA255 Pin | Function           |  |  |  |  |  |  |

|------------|--------------------|--|--|--|--|--|--|

| GPIO84     | Clock (100kHz max) |  |  |  |  |  |  |

| GPIO83     | Data               |  |  |  |  |  |  |

The DS1338 RTC also contains 56 bytes of RAM, which can be used for any user data that needs to be recoverable on power-up.

To ensure the DS1338 RTC doesn't lose track of the date and time when the 5V supply is powered-down, the onboard battery must be fitted. See the section <u>Battery backup</u>, page <u>73</u>, for details.

# Watchdog timer

The PXA255 contains an internal watchdog timer, which can be used to protect against erroneous software. Timeout periods can be adjusted from 271ns to 19 minutes 25 seconds. When a timeout occurs the board is reset. On reset the watchdog timer is disabled until enabled again by software.

For further details see the Arcom Operating System Technical Manual and the PXA255 Developer's Manual on the Development Kit CD.

## Memory

The VIPER has four types of memory fitted:

- 1MB of bootloader FLASH containing Redboot to boot embedded Linux or VxWorks, or Eboot to boot Windows CE.

- A resident FLASH disk containing the OS and application images.

- SDRAM for system memory.

- 256KB Static RAM (SRAM).

A 1MB Bottom Boot FLASH EPROM device, arranged as 512Kbit x 16, is used as the bootloader FLASH. It holds Redboot (for embedded Linux or VxWorks) or Eboot (for Windows CE), together with configuration information. When the microprocessor comes out of reset it boots the relevant bootloader from here, which in turn boots up the OS from the FLASH memory/silicon disk. Whenever the Bootloader FLASH memory is accessed the FLASH access LED illuminates.

#### FLASH memory/silicon disk

The VIPER supports 16MB or 32MB of Intel StrataFLASH memory for the OS and application images. The FLASH memory is arranged as 64Mbit x 16-bits (16MB device) or as 128Mbit x 16-bits (32MB device) respectively.

The FLASH memory array is divided into equally sized symmetrical blocks that are 64-Kword in size. A 128Mbit device contains 128 blocks, and 256Mbit device contains 256 blocks. Flash cells within a block are organized by rows and columns. A block contains 512 rows by 128 words. The words on a row are divided into 16 eight-word groups.

The PXA255 GPIO14 pin is connected to the FLASH memory status output. This pin can be used to generate an interrupt to indicate the completion of a CFI command.

Whenever the FLASH memory is accessed the FLASH access LED illuminates.

#### SDRAM interface

There are two memory configurations supported by the VIPER: 16MB or 64MB of SDRAM located in Bank 0. The SDRAM is configured as 4MB x 32-bits (16MB) or 16MB x 32-bits (64MB), by 2 devices with 4 internal banks of 1MB or 4MB x 16-bits.

These are surface mount devices soldered to the board and cannot be upgraded. RedBoot (embedded Linux and VxWorks) automatically detects the amount of memory fitted to the board, and configures the SDRAM controller accordingly. For Windows CE applications the SDRAM memory will always be 64MB.

The SDRAM controller supports running the memory at frequencies between 50MHz and 99.5MHz (default). This can be configured to achieve the optimum balance between power consumption and performance.

#### Static RAM

The VIPER has a 256KB SRAM device fitted, arranged as 256Kbit x 8-bits. Access to the device is on 16-bit boundaries; whereby the least significant byte is the SRAM data and the 8-bits of the most significant byte are don't care bits. The reason for this is that the PXA255 is not designed to interface to 8-bit peripherals. This arrangement is summarized in the following data bus table:

|            | Most Significant Byte |     |     |     |     |     |    | Least Significant Byte |    |    |      |        |    |    |    |    |

|------------|-----------------------|-----|-----|-----|-----|-----|----|------------------------|----|----|------|--------|----|----|----|----|

|            | D15                   | D14 | D13 | D12 | D11 | D10 | D9 | D8                     | D7 | D6 | D5   | D4     | D3 | D2 | D1 | D0 |

| Don't Care |                       |     |     |     |     |     |    |                        |    |    | SRAN | 1 Data | à  |    |    |    |

The SRAM is non-volatile while the onboard battery is fitted.

### *CompactFLASH*

The CompactFLASH connector PL5 is interfaced to Slot 0 of the PXA255 PC card controller, and appears in PC card memory space socket 0.

This is a hot swappable 3.3V interface, controlled by the detection of a falling edge on GPIO32 when a CompactFLASH card has been inserted. On detection set GPIO82 to logic '1' to enable the 3.3V supply to the CompactFLASH connector. The CompactFLASH (RDY/nBSY) signal interrupts on GPIO8.

| Address                 | Region name                     |

|-------------------------|---------------------------------|

| 0x2C000000 – 0x2FFFFFFF | Socket 0 Common Memory Space    |

| 0x28000000 – 0x2BFFFFFF | Socket 0 Attribute Memory Space |

| 0x24000000 – 0x27FFFFFF | Reserved                        |

| 0x20000000 – 0x23FFFFFF | Socket 0 I/O Space              |

Many CF+ cards require a reset once they have been inserted. The CF reset must remain high (inactive) for 1ms after power has been applied to the CF socket, and then go low (active) for at least 10µs.

To reset the CompactFlash socket independently set the CF\_RST bit to '1' in the ICR register located at offset 0x100002 from CS5 (0x14000000). To clear the CompactFlash reset write a '0' to the CF\_RST bit.

# Interrupt configuration and reset register [ICR]

| Byte lane |    | Most Significant Byte |    |    |    |    |   |      | Least Significant Byte |   |   |   |           |       |              |        |

|-----------|----|-----------------------|----|----|----|----|---|------|------------------------|---|---|---|-----------|-------|--------------|--------|

| Bit       | 15 | 14                    | 13 | 12 | 11 | 10 | 9 | 8    | 7                      | 6 | 5 | 4 | 3         | 2     | 1            | 0      |

| Field     | -  | -                     | -  | -  | -  | -  | - | -    | -                      | - | - | - | CF<br>RST | R_DIS | AUTO_<br>CLR | RETRIG |

| Reset     | Х  | Х                     | Х  | Х  | Х  | Х  | Х | Х    | 0                      | 0 | 0 | 0 | 0         | 0     | 0            | 0      |

| R/W       | -  | -                     | -  | -  | -  | -  | - | -    | R                      |   |   |   | R/W       |       |              |        |

| Address   |    |                       |    |    |    |    | 0 | x141 | 14100002               |   |   |   |           |       |              |        |

# **ICR Bit Functions**

| Bit   | Name     | Value | Function                                                                   |

|-------|----------|-------|----------------------------------------------------------------------------|

| 0     |          | 0     | No interrupt retrigger (embedded Linux and VxWorks).                       |

| 0     | RETRIG   | 1     | Interrupt retrigger (Windows CE).                                          |

|       |          | 0     | No auto clear interrupt / Toggle GPIO1 on new interrupt.                   |

| 1     | AUTO_CLR | 1     | Auto clear interrupt / Low to high transition on GPIO1 on First Interrupt. |

| 2     | R_DIS    | 0     | Board reset normal                                                         |

|       | -        | 1     | Board reset disable                                                        |

| 3     | CF_RST   | 0     | CompactFlash reset by board reset                                          |

|       |          | 1     | Reset CompactFlash                                                         |

| 4 - 7 | -        | Х     | No function.                                                               |

## Interrupt assignments

#### Internal interrupts

For details on the PXA255 interrupt controller and internal peripheral interrupts please see the PXA255 Developer's Manual on the Development Kit CD.

#### External interrupts

The following table lists the PXA255 signal pins used for generating external interrupts.

|              | PXA255 Pin | Peripheral                  | Active                         |

|--------------|------------|-----------------------------|--------------------------------|

|              | GPIO0      | Ethernet                    | _ <b>f</b>                     |

| $\bigotimes$ | GPIO1      | PC/104 interrupt controller | See PC/104 interrupts, page 30 |

| $\bigotimes$ | GPIO2      | USB                         | <b>~</b> _                     |

| $\bigotimes$ | GPIO3      | COM5                        | _ <b>f</b>                     |

| <b>V</b>     | GPIO4      | COM4                        | _ <b>f</b>                     |

|              | GPIO8      | CompactFLASH RDY/nBSY       | Ready = 🕂 ,Busy = 🚽            |

|              | GPIO14     | FLASH (OS)                  | Ready = 🕂 ,Busy = Վ            |

|              | GPIO32     | CompactFLASH card detect    | <b>~</b>                       |

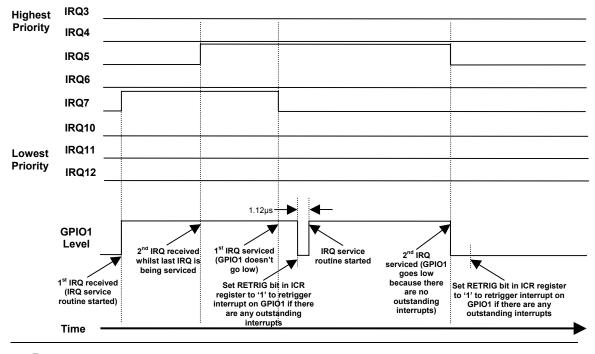

#### PC/104 interrupts

The PC/104 interrupts are logically OR'ed together so that any interrupt generated on the PC/104 interface generates an interrupt input on GPIO1.

The PC/104 interrupting source can be identified by reading the PC104I1 & 2 registers (PC104I2 is not available under Windows CE as all interrupt sources are fully utilized) located at offset 0x100000 and 0x100004 respectively from CS5 (0x14000000). The registers indicate the status of the interrupt lines at the time the register is read. The relevant interrupt has its corresponding bit set to '1'. The PXA255 is not designed to interface to 8-bit peripherals, so only the least significant byte from the word contains the data.

## *PC/104 interrupt register [PC104I1]*

| Byte lane |    | Most Significant Byte |    |    |    |    |   |   | Least Significant Byte |       |       |      |      |      |      |      |

|-----------|----|-----------------------|----|----|----|----|---|---|------------------------|-------|-------|------|------|------|------|------|

| Bit       | 15 | 14                    | 13 | 12 | 11 | 10 | 9 | 8 | 7                      | 6     | 5     | 4    | 3    | 2    | 1    | 0    |

| Field     | -  | -                     | -  | -  | -  | -  | - | - | IRQ12                  | IRQ11 | IRQ10 | IRQ7 | IRQ6 | IRQ5 | IRQ4 | IRQ3 |

| Reset     | Х  | Х                     | Х  | Х  | Х  | Х  | Х | Х | 0                      | 0     | 0     | 0    | 0    | 0    | 0    | 0    |

| R/W       | -  | -                     | -  | -  | -  | -  | - | - | R/W                    |       |       |      |      |      |      |      |

| Address   |    | 0x14100000            |    |    |    |    |   |   |                        |       |       |      |      |      |      |      |

## PC/104 interrupt register [PC104I2] (not available under Windows CE)

| Byte lane | Most Significant Byte Least Significant Byte |    |    |    |    |    |   |   |   |   |   |   |   |       |       |      |

|-----------|----------------------------------------------|----|----|----|----|----|---|---|---|---|---|---|---|-------|-------|------|

| Bit       | 15                                           | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2     | 1     | 0    |

| Field     | -                                            | -  | -  | -  | -  | -  | - | - | - | - | - | - | - | IRQ15 | iRQ14 | IRQ9 |

| Reset     | Х                                            | Х  | Х  | Х  | Х  | Х  | Х | Х | 0 | 0 | 0 | 0 | 0 | 0     | 0     | 0    |

| R/W       | -                                            | -  | -  | -  | -  | -  | - | - |   |   | R |   |   |       | R/W   |      |

| Address   | 0x14100004                                   |    |    |    |    |    |   |   |   |   |   |   |   |       |       |      |

The ICR Register located at offset 0x100002 from CS5 (0x14000000) must be set-up correctly for the OS running. The PC/104 interrupts are signaled and handled slightly differently between embedded Linux / VxWorks and Windows CE. See the following relevant subsections for specific PC/104 details for the target OS.

Interrupt configuration and reset register [ICR]

| Byte lane |            | Most Significant Byte |    |    |    |    |   |   |       | Least Significant Byte |   |   |            |       |             |         |  |

|-----------|------------|-----------------------|----|----|----|----|---|---|-------|------------------------|---|---|------------|-------|-------------|---------|--|

| Bit       | 15         | 14                    | 13 | 12 | 11 | 10 | 9 | 8 | 7     | 6                      | 5 | 4 | 3          | 2     | 1           | 0       |  |

| Field     | -          | -                     | -  | -  | -  | -  | - | - | -     | -                      | - | - | CF_<br>RST | R_DIS | AUTO<br>CLR | -RETRIG |  |

| Reset     | Х          | Х                     | Х  | Х  | Х  | Х  | Х | Х | 0     | 0                      | 0 | 0 | 0          | 0     | 0           | 0       |  |

| R/W       | -          | -                     | -  | -  | -  | -  | - | - | R R/W |                        |   |   |            |       |             |         |  |

| Address   | 0x14100002 |                       |    |    |    |    |   |   |       |                        |   |   |            |       |             |         |  |

### **ICR Bit Functions**

| Bit   | Name     | Value | Function                                                                                                       |

|-------|----------|-------|----------------------------------------------------------------------------------------------------------------|

| 0     | RETRIG   | 0     | No interrupt retrigger (embedded Linux and VxWorks)                                                            |

| U     |          | 1     | Interrupt retrigger (Windows CE)                                                                               |

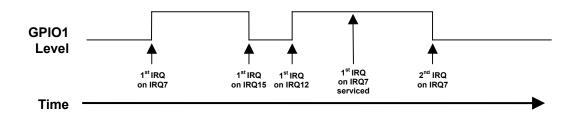

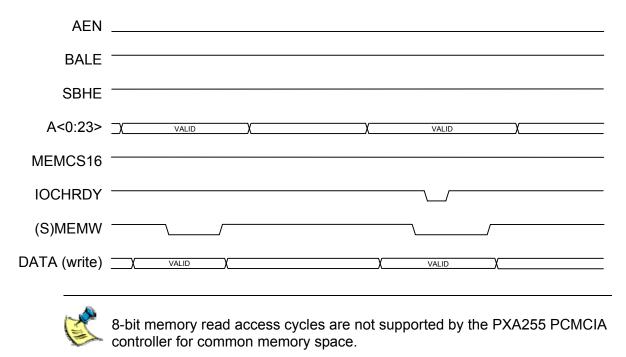

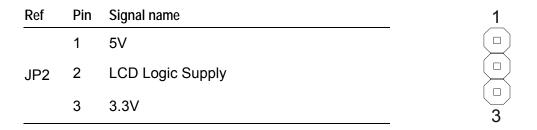

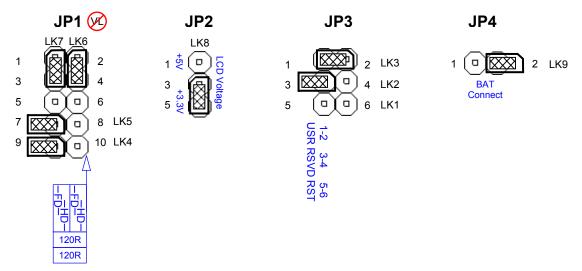

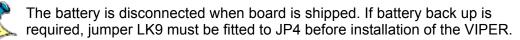

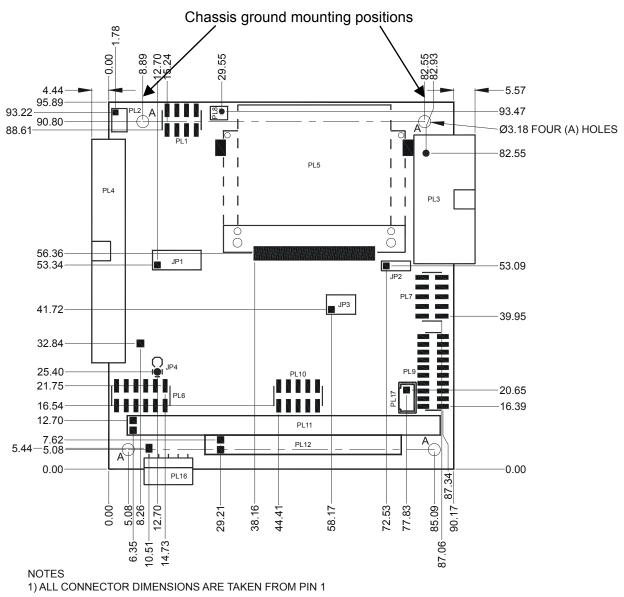

| 1     |          | 0     | No auto clear interrupt / Toggle GPIO1 on new interrupt (embedded Linux and VxWorks)                           |